3 ポートS パラメータ解析を活用した、GaAs MMIC SPDT SW 使用 「広帯域 IC SW 回路」の性能最適化と応用製品の実践開発指針

Aug.16, 2009 Mr. Endo

# 1. 序文

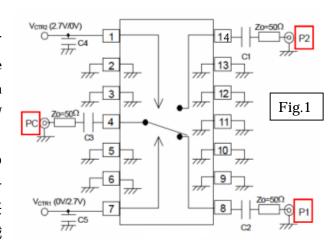

3ポートSパラメータ解析を活用して、Fig.1 に示す GaAs MMIC の SPDT[Single Pole Double Throw] SW - NLG1512V を使用した高 Isolation 広帯域 SW の、高周波特性 - 解析評価方法と SW ON/OFF 性能の最適化について解説する。

この SW 回路は、周波数 100MHz - 3GHz のVHF 帯 / UHF 帯信号を ON/OFF する「RF 信号 切替回路」や、 型 ATT 回路を組み合わせて任意の 2 進数減衰量 (0dB - 63dB)を得る「広帯域

減衰器」に適する。なお、同 IC SW を適用した実践回路の設計方法を後述する。

- 2. 広帯域 IC SW 等価回路 [50 系] の作成

- (1) 広帯域回路の形成に必要な分布定数線路の マイクロストリップライン[MSL: Micro-Strip Line]の 設計について簡単に触れる。

- (2) SNAP のコーティリティ機能から「マイクロストリップの特性インピーダンス」を呼び出して、Fig.2 のようにプリント基板のパラメータを記入すると、所望の特性インピーダンス Zo を有する MSL の線路幅等を求めることができる。

- (3) ここでは、IC SW や周波数特性補償回路の チップ部品を MSL に実装するために、MSL の両側に MSL の線路幅と略同じ幅のクリアラン

MSL: Micro-Strip Line ・NAPユーティリティ く マイクロストリップ\*> × 1.72u 誘電体の厚み[m] 1m 導体抵抗率 導体の厚み[m] 35u 周波数[Hz] 1G 誘電率 3.34 ストリップ幅[m] 2.2m 誘電正接 特性インピーダンス 51.3145 [オーム] 2,62036 実効誘電率 Fig.2 0.727131 [dB/m] 伝送損失 0.185198 [m] 基板上の波長 デ"フォルト 計算 クリア クリップ。

Simulation準備として使用線路MSLの諸元設定と特性

スを介して、ベタ GND を設けることを考慮して、MSL の特性インピーダンス Zo を規定の 50 に対して、約 2 - 3%程度大きく選定する。

- (4) それはMSL両側のGNDに よって MSL の特性インピーダ ソスが 2 - 3%低下することを 補償するためである。

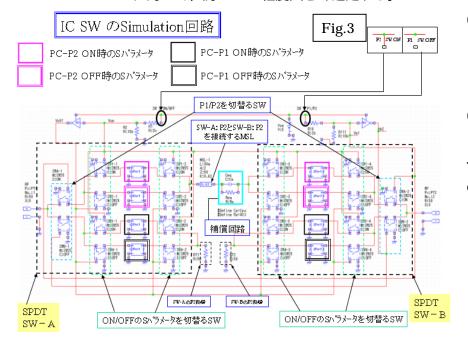

- (5) シミュレーション回路全体を Fig.3 に示す。IC SW は、3 ポートネットワ ーク回路で表される。即ち、2 つの入力ポート [端子](P1、P2)と1つの出力ポート(PC)を有し、

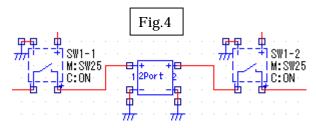

各ポートに対して ON (入出力間導通) / OFF (入出力間遮断)の2つの Sパラメータが用意されているので、各入力ポート毎に 2 系統の SW 切換回路 [Fig.4 参照]を「集中定数素子群¥電圧制御スイッチ」を使用して形成する。

- (6) IC SW の入出力は、SW を通過する高周波信号に対して可逆特性を有するので、2つの SPDT SW を対向して縦続し、SW の ON/OFF アインレーションを向上する。 具体的には、 SW[SPDT SW-A]では出力端を入力ポートとし、2つの入力端を各々出力ポートとして機能させる。出力側の IC SW[SPDT SW-B]では、通常通り2つの入力端をそれぞれ入力ポートとし、出力端を出力ポートとして機能させる。

- (7) SPDT SW-A のポート P2 と SPDT SW-B のポート P2 を伝送線路 MSL で接続し、その間に周波数特性補償回路を挿入する。これによって、SW 回路を ON に働かせると同時に、目標帯域内の通過特性を平坦にする。

- (8)SPDT SW-A のポート P1 と SPDT SW-B のポート P の夫々は、50 終端で接続して SW 回路 OFF のときに、発生する漏洩信号を終端負荷に吸収させる。これによって、SW の遮断性能を達成して ON/OFF のアイソレーションを向上させる。

(9)各電圧制御 SW はマトリックス状に結線 され、インバータを介して電源ラインに接続された SW [結線]をショート/ オープソにすることがよートの ON/OFF の S パラメータを同時に切まる。

- 3 . 広帯域 IC SW 等価回路の S パラメータ解析

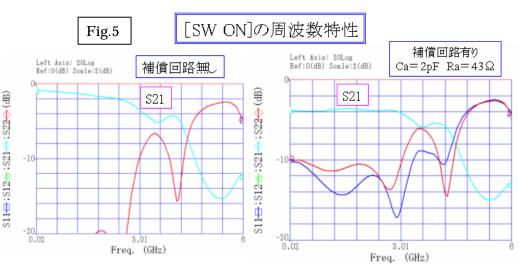

- (1) SW ON の通過特性を Fig.5 に示す。MSL に 周波数特性補償回路を挿入して、SNAP のチューニング機能で、その定数を最適化することによって、20MHz 3GHz の広帯域に亘って、通 過損失の帯域内偏差を約 0.5dB 程度に向上させることが出来た。

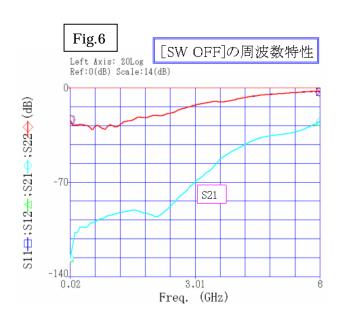

- (2) SW OFF の通過特性を Fig.6 に示す。3GHz 以下で通過損失は-70dB 以下を示し、上記の SW ON の通過損失と対比してみると、SW 回路の ON/OFF アインレーションは、20MHz 3GHz の広帯域に亘って、約 65dB 以上と優れた性能を表している。

- 4. 広帯域 IC SW コア回路 [75 系] の基礎検証

Fig.7

#### [A]広帯域 IC SW コア回路の試作評価

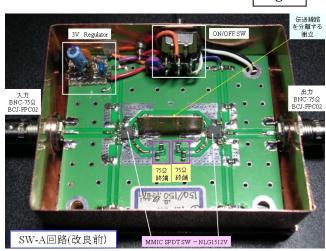

GaAs MMIC の SPDT SW - NLG1512V を使用した試作装置を Fig.7 に示す。 3V の DC 電圧をトグル SW にて切替えて、制御端子 VCTR1 / VCTR2 に印加することにより、RF 信号の通過を経路を PC P1 / PC P2 に高速で切替えることが出来る。トグル SW の代わりに、論理信号(TTL や ECL)で切替制御すれば、IC SW の応答性能を考慮して、数 ns 程度の切替制御は十分に可能である。

Fig.8

A力 3/7 7/7 2

A 力 3/7 7

A

SW 切替制御端子 VCTR1 / VCTR2 直近には、数 100pF - 1,000pF の RF バイパス用のチッ プ・コンデンサを GND に接地することにより、SW の ON / OFF の周波数特性を向上させる。

IC SW の ON/OFF アイソレーションを向上させるためには、2 つの切替経路 PC P1 / PC P2を分離するシールド板や、MSL と同軸コネクタの伝播モードの違いによる RF 信号の反射・放射を

低減する入出力同軸コネクタ部分のシールドが有効 [ Fig.8 ] であることを確認した。

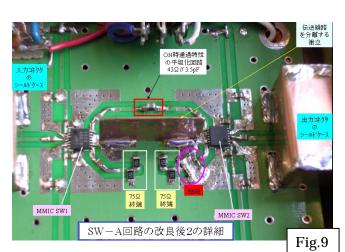

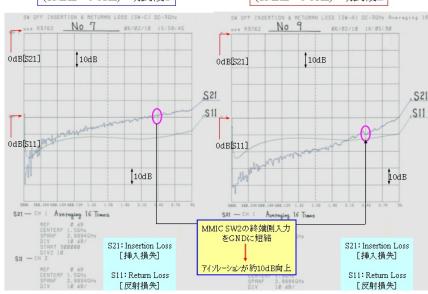

Simulation 解析には反映されないが、実験検証では、SPDT SW - B [ 出力側の RF 切替 IC SW2 ] 側の反射終端 75 を GND に短絡 [ Fig.10 ] することにより、SW OFF 時の減衰量を 10dB 近く向上できることが、分かっている。これは入力側の SPDT SW - A [ RF 切替 IC SW 1 ] の終端抵抗 75 と SPDTSW

SW-A回路OFF特性 (1MHz-3GHz) 改良後1 Fig.10

SW-A回路OFF特性 (1MHz-3GHz) 改良後2

- B [ 出力側の RF 切替 IC SW2 ] の反射終端 75 が隣接することによって、両者の電磁誘導結合或いはアースポ テンシャル結合が微少に生じ、SWOFF 時の両 IC SW が僅少に干渉することを、防いでいる[Fig.10] ものと推定される。

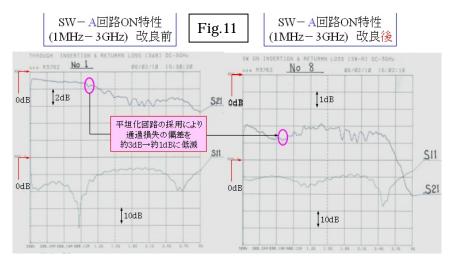

ICSW1 と ICSW2 の導通側の伝送路 MSL の中途にイコライザ回路を挿入して、

通過周波数特性を補償することにより、Fig.11 に示すように通過損失の偏差を約 3dB から約 1dBに低減できる。

[B] 広帯域 IC SW コア等価回路の Simulation 解析と試作評価の比較検証

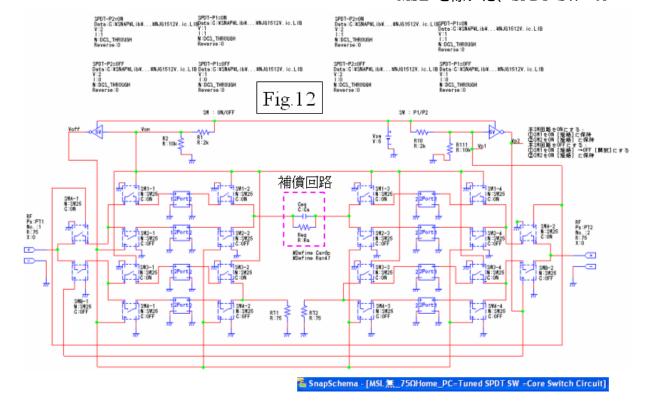

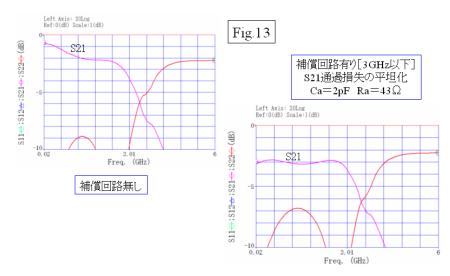

導通側/遮断側を接続する MSL を除いた、SPDT SW - A

[入力 SW1] SPDT SW-B [出力 SW2] および周波数特 性補償用のイコライザで構成され る、等価回路[Fig.12]を形成す る。

SW ON 時の通過減衰周波数 特性を、補償回路無しの場合と、 補償回路有りの場合を比較し

て Fig.13 に示す。

使用周波数 3GHz 以下の帯域に於いて、通過 減衰量の帯域偏差を、補償回路無の約 3dB か ら補償回路有の約 0.5dB に、大きく低減させ ている。

補償回路の働きによる、SW ON 時の通過 減衰量 - 帯域偏差の改善効果は、前記の試作 評価の結果と、上記 Simulation 解析の改善 効果が、実に良く一致している。

Eeft Axis: 20Log

Ref:0(dB) Scale:13(dB)

Fig.14

(9p)

-65

-65

-130

0.02

3.01

Freq. (GHz)

SW OFF 時の通過減衰量 [ 遮断 ] は、前記

の試作評価の SW-A 改良後 2 の減衰特性 [ 3GHz 以下 ] と、上記の Simulation 解析の減衰 特性が、相似していることが判る。

## 5. 広帯域 IC ATT コア回路 [75 系] の基礎検証

## [A]広帯域 IC ATT コア回路の試作評価

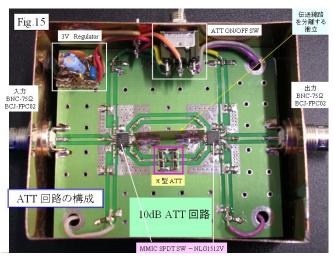

前記の広帯域 IC SW コア回路において、入 力側の SPDT SW - A [ RF 切替 IC SW 1 ] の 終端抵抗 75 と SPDTSW - B [ 出力側の RF 切替 IC SW2 ] の終端抵抗 75 を接続する替わ りに、型 ATT 回路を介して両端を接続する。

Fig.15 の基板に於いて、入力コネクタ IC SW1 上側 MSL IC SW2 出力コネクタの RF 信号伝

10dBATT回路減衰側特性 (1MHz-3GHz)

送路が導通側[非ATT側]となり、入力コネクタ IC SW1 下側 MSL[途中に 型ATT を含む] IC SW2 出力コネクタの RF 信

号伝送路が ATT 側になる。

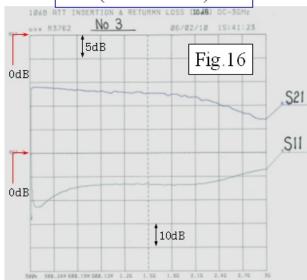

10dB ATT を 型 ATT 回路で構成した、広 帯域 IC 10dB ATT 回路の ATT 側の通過減衰 特性を Fig.16 に示す。

3GHz以下の通過帯域偏差は概ね6dBあることが分かる。

[B] 広帯域 IC ATT コア等価回路の Simulation 解析と試作評価の比較検証

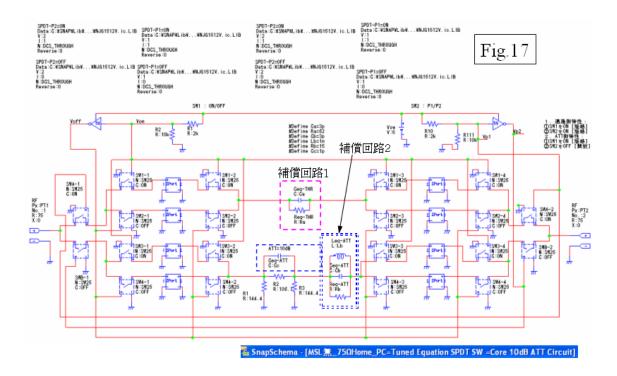

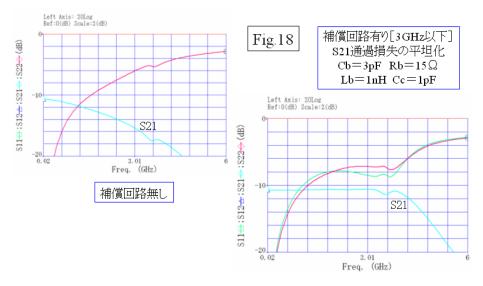

導通側/遮断側を接続する MSL を除いた、SPDT SW - A [入力 SW1] SPDT SW - B [出力 SW2] および周波数特性補償回路で構成される、10dB ATT 等価回路[Fig.17]を形成する。

上記 10dB ATT 等価回路の ATT 側の減衰特性を Fig.18 に示す。3GHz 以下における減衰特性の帯域偏差は、補償回路 2 無しで約 5dB 有り、前記の試作評価[Fig.16]の偏差約 6dB に相似していることが分かる。

試作評価で実際に検証で きていないが、

Simulation 解析[Fig.18] では、補償回路2の働き で、減衰特性の偏差を約 1dB に低減できるものと 推測される。

## 6 . デジタル衛星放送受信装置用 広帯域 SW 装置の設計開発

#### [1]機能

BS IF 信号 / CS IF 信号を切替え、併せて同 RF 信号レベルを任意に減衰調整する。

# [2]背景

地上デジタル TV 放送の 2011 年 7 月完全以降が終了すると、次世代のデジタル放送普及の目玉政策として、大容量 Hi-Vision 衛星放送 [ HDTV を 50ch - 100ch 同時放送 ] を 2015

年頃に導入する、準備を関係機関で推進している。 さらには 2020年頃の実用化を目指して、地上デジタル放送の 4 倍の解像度を有する超 Hi-Vision 放送を、衛星放送する研究開発も行われている。

このような背景に対して、Hi-Vision 受信機に各種デジタル TV 放送 [ 地デジ / BS デジタル / CS デジタル ]を選択受信させるためには、デジタル衛星放送をアンテナ受信した BS IF 信号 / CS IF 信号を切替える広帯域 SW 装置が必要になる。

各種デジタル放送は伝播経路が 異なるために、その受信レベルが 大幅に異なる。そのために切替選 択した RF 信号レベルを、広帯域 SW ATT により所定レベルに調整

20dB結合Output[50Ω]

して、適切な信号レベルを Hi-Vision 受信機に入力することが必要になる。

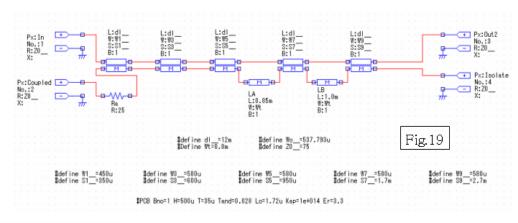

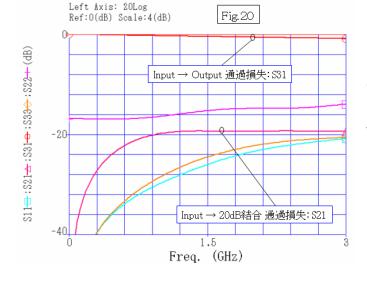

## [3]20dB 広帯域方向性結合器の設計

SNAP デザイン機能を利用して、低域遮断周波数 685MHz の広帯域 20dB 方向性結合器 [Fig.19]を設計する。この方向性結合器は Fig.20 に示すように、BS/CS の IF 周波数帯域 約 1.2 GHz - 2.7GHz に亘って、結合度約 20dB の平坦特性を得ている。

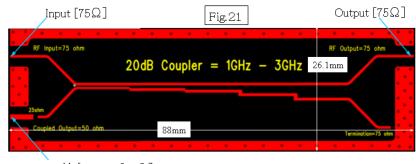

この広帯域 20dB 方向性結 合器の形状 [ MSL の配置・結 合間隔等 ] を下に、PCB 基板 パターンを CAD 設計した結 果を Fig.21 に示す。

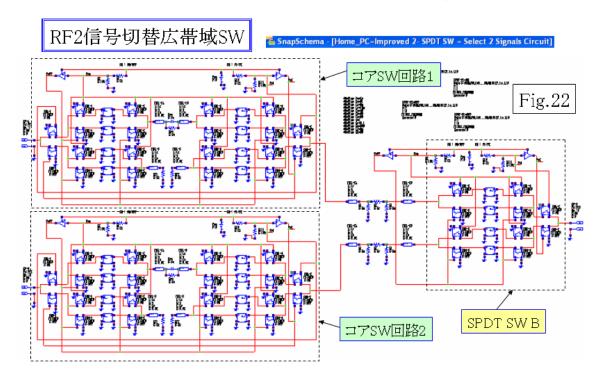

[4]RF2信号を切替える広

# 帯域 高分離度 SW の設計

BS / CS IF 信号を切替える広帯域 SW(50 系)は、2つの入力ポートP1、P2 [切替対象となる2つの RF 信号の入力端子]に接続された、コア SW 回路 1(前記の広帯域 SW コア回路 Fig.12と同一構成)とコア SW 回路 2、および両コア SW 回路 1、2の出力を切替える SPDT SWB で構成される。[Fig.22]

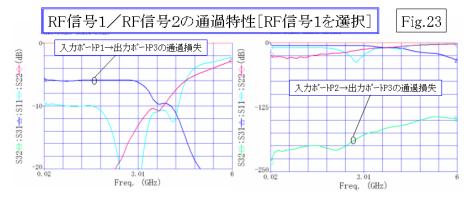

RF 2 信号の切替特性を S パラメータ解析で調べてみると、Fig.23 に示すように 3GHz 以下の帯域に於いて、SW ON 時の通過損失は約 6dB [偏差 0.5dB 以下 ] SW OFF 時の通過損失は約 150dB 以上となり、RF 2 信号の切替アインレーションは 140dB 以上と極めて良好な SW 性能が期待できる。

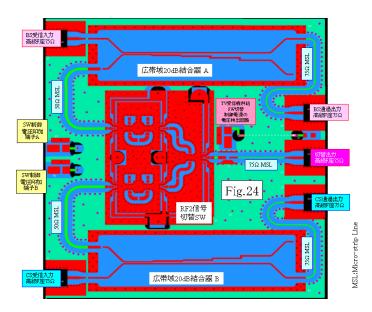

この広帯域 SW および前記広帯域 20dB 方向性結合器を一緒に構成した、広帯域 SW 装置のPCB レイアウトを Fig.24 に示す。なお参考までに、

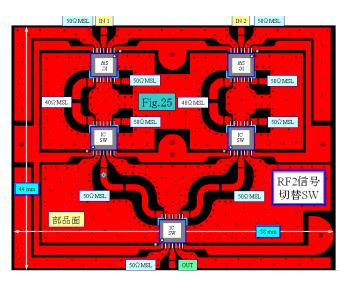

RF2信号切替SWの部品実装イメージ図を Fig.25 に示す。

# [5]広帯域SW2進数ATT PFA力 回路の設計

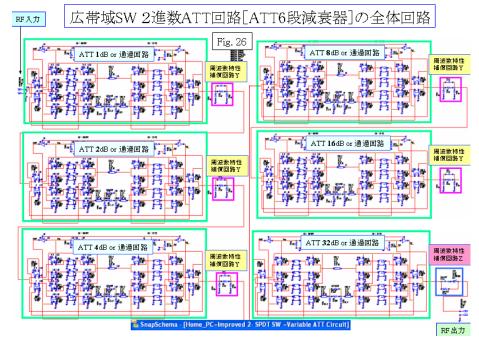

広帯域SW2進数ATT回路は、前記の広帯域IC ATTコア回路を50系で形成した、ユニットATTを6段に縦列接続した構成になっている。

その広帯域 SW 2 進数 ATT 回路の等価回路(Fig.17)を、

#### ATT OdB[全段:非ATT側]の通過特性

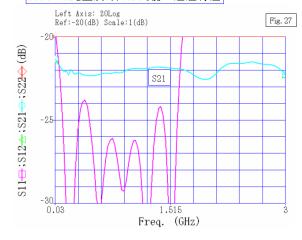

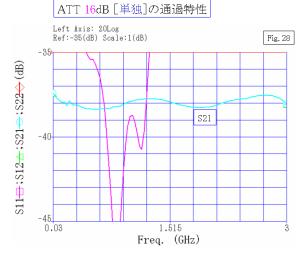

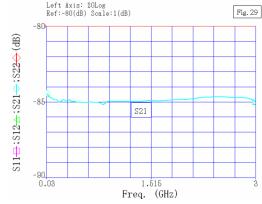

S パラメータ解析した、代表的な周波数特性を Fig,27 -Fig.29 に示す。

通過 ATT 0dB で、6 段の ATT ユニットの導通側を全て 通過した場合の通過損失は約 22dB 「帯域内偏差 0.5dB 以下 ] となり、この通過損失が ATT 0dB の基 準値(Fig.27)になる。

ATT 16dB の条件では、5 段目の ATT ユニットで 16dB ATT 側を通過し、その他の ATT ユニットでは全 て導通側を通過する。このときの全通過損失は約 38dB(=基準值 22dB + ATT 16dB、帯域内偏差 1dB 以下)になっている。

ATT 63dB の条件では、6 段の ATT ユニットの ATT 側を全て通過する。このときの全通過損失は約 85dB(=基準值 22dB + ATT 63dB、帯域内偏差 1dB 以下)になっている。

ATT 63dB=1dB+2dB+4dB+8dB+16dB+32dB の通過特性

CS IF 信号の信号レベルを、高速(1us 以下)に

しが得られた。

各ATTのON/OFF

且つ高精度(ATT 減衰量精度 1dB 以内)に任意「論理的]に 制御できると推測される。

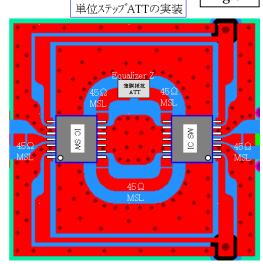

なお、広帯域 SW 2 進数 ATT 回路の PCB CAD 設計を Fig.30 に示す。前記の広帯域 IC ATT コ ア回路を、MSL で接続された1 よって、広帯域 SW2進数 ATT 回路は、BS/

SPDT IC SW を 2 つ直列に接続した構成の ATT

コニットを、6段に縦列接続した広帯域SW2進数ATT

回路は、30MHz - 3GHzの広帯域に亘って、高精

度に ATT [通過減衰量]を2進数制御できる見通

6ステップ。ATT回路基板設計[全体] 基板種別:CS-3376C 板厚=0.5mm SW¥Oct.19\_2006=基板設計¥SW¥6\_Stage\_ATT.pcb = PowerPGB Fig.30 MSL: Micro-Strip Line (2) 半田面 95mm

(1) 部品面

6ステップ。ATT回路基板設計

Fig.31

MSLによる段間接続 X assignment X

ライザ (周波数補償)回路)を介して、6 段に縦列接続されている。参考として、単位ステップ ATT [ 広帯域 IC ATT コア回路 ] の部品実装配置を FIg.31 に示す。

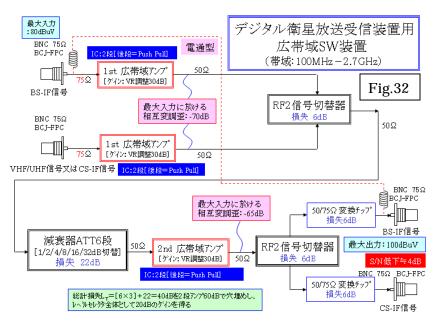

# [6] 広帯域 SW 装置の全体構成

同SW 装置の構成(コンセプト)を Fig.32 に示す。

SPDT IC SW を適用した広帯域 SW からなる、RF 2 信号切替器

[Fig.22]および広帯域 SW 2 進数 ATT 回路 (減衰 ATT 6 段) [Fig.26]を基本回路とし、それに RF 信号の減衰量を補償する、広帯域アンプを適切に組み合わせることによって、次世代デジタル衛星放送受信装置に適合する広帯域 SW 装置を、SNAP Simulation 解析の活用によって実現できる見通しを得た。

#### 7. GaAs MMIC SPDT SW 使用 した「広帯域 IC SW 回路」の纏め

- (1)3ポートSパシータの解析を縦横無尽に駆使することによって、広帯域 IC SW 応用回路の適応範囲を顕著に拡大すると共に、次世代デジタル衛星放送時代に適した新規製品開拓を、高性能・高品質で且つスピーディに達成できることを、明らかにした。

- (2) S パラメータ解析は、数 MHz 数 GHz 以上に渡る広帯域の周波数 領域に於いて、数 dB から数 100dB 以上の超高ダイナミック・レンジに及んで、

GaAs MMIC で構成される IC SW 等の特性を、高精度且つ高速に、さらに柔軟に解析できることを検証した。

(3)デジタル放送・通信時代の機器設計に、SNAP シミュレータは最適であること、その上、機器の試作評価と比較検証することで、機器の性能を最適化、高性能化できる能力を備えていることを、立証することが出来た。

- 以上 -