# 低雑音増幅器の設計手法

トランジスタ増幅器の雑音指数は、トランジスタの入力に接続されたソースインピーダンスの関数になります。一般に、このインピーダンスを示す反射係数は $\Gamma$  opt と呼ばれており、このインピーダンスに入力側のインピーダンス(ソースインピーダンス)を整合させることで、トランジスタ内部で発生する雑音量を最小にすることができます。しかし残念なことに、多くの場合このインピーダンスは、トランジスタの最大有能電力利得の得られるインピーダンスの値とは若干異なっており、このために電力整合を行うと雑音が最小にならず、また雑音整合を行うと、入力リターンロスが悪くなる、という厄介な問題が発生します。この問題を解決するためには、雑音整合と入力リターンロス整合を連立して考え設計する必要があります。この問題は、シリーズフィードバックテクニックを用いることで、ほぼ解決することができます。特にFET のLNAの場合この手法が有効になります。

## 1.1.電力整合点と雑音整合点

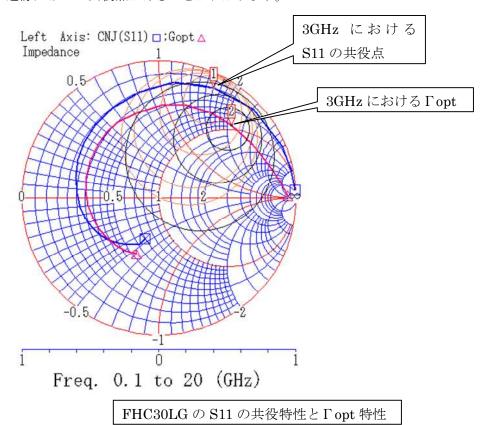

図 1 に例として、FHC30LG (HEMT) の場合の S11 の共役特性と  $\Gamma$  opt 特性を示します。3GHz における特性に着目すると、S11 の共役点はマーカ 1 のようになり、 $\Gamma$  opt はマーカ 2 のようになります。マーカの周りにある円は、それぞれゲインサークルと NF サークルを示しています。このトランジスタの場合、S11 の共役点と  $\Gamma$  opt は図の如く離れており、NF サークルが 2dB 円の近傍に S11 の共役点があることがわかります。

### 1-1-1電力整合のみを考慮した場合

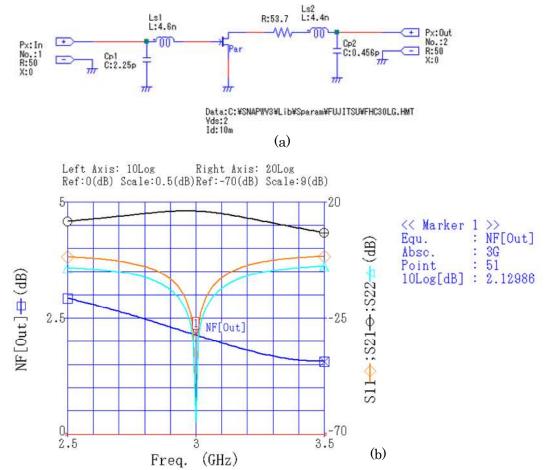

最大有能電力利得の設計式に準じて、電力整合だけを考慮した整合回路設計を行ってみると、図 2(a)のような構成の回路を設計することができます。この回路のシミュレーションを行うと、図 2(b)のような特性となり、入出力特性は完全に整合していることがわかります。しかしながら、雑音指数は 2.1dB 程度あり、低雑音増幅器としては特性を満足していないと言えます。

図2 電力整合のみを考慮した回路

# 1-1-2雑音整合のみを考慮した場合

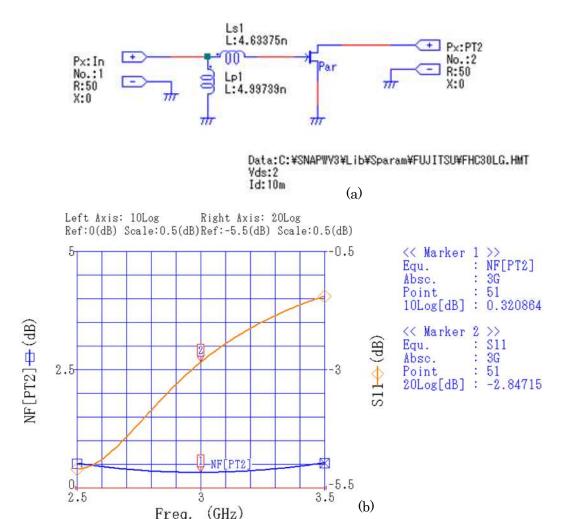

今度は図 3(a)のように、3GHz において入力側をトランジスタの $\Gamma$  opt に整合させた回路を作成してみます。シミュレーション特性は図 3(b)のようになります。雑音指数は 0.32dB となり、トランジスタ単体の NFmin 値に一致します。しかしながら、リターンロスはわずか 2.85dB しかなく、電力整合は満足していないことがわかります。

図3 雑音整合のみを考慮した回路

# 1.2.ソースリアクタンスの装荷による特性の変化

前述のように、一般にトランジスタでは電力整合の最適点と雑音整合の最適点がずれていることから、そのままでは両者を同時に満足させる整合回路を設計することは、難しいものがあります。そこで、両者を同時に満足させる手法の一つとして、トランジスタにリアクタンスを装荷し、見かけ上のトランジスタの特性を電力整合の最適点と雑音整合の最適点が近づくように変更する方法があります。

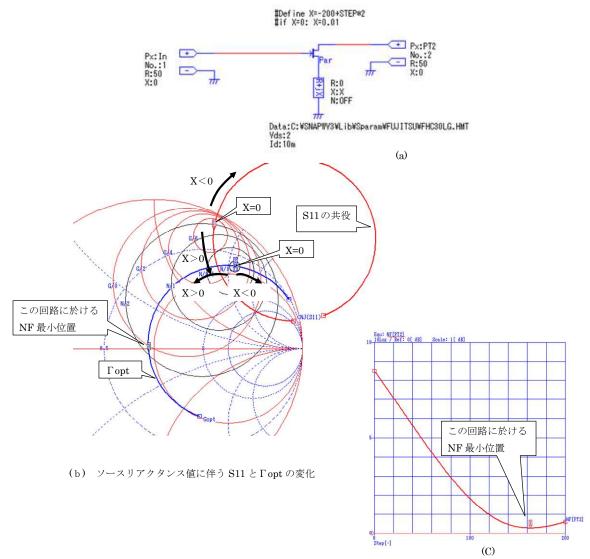

図 4 はソースにリアクタンスを挿入した状態で S パラメータのシミュレーションを行っている回路です。このシミュレーション回路で、ソースリアクタンスを-200  $\Omega$  から+200  $\Omega$  まで可変した場合の、全体の S11 の共役値の変化と新しい  $\Gamma$  opt の軌跡を調べてみます。図 4-b がその結果で、S11 の共役値はソースリアクタンスがない場合の値を起点として、負のリアクタンスを挿入すると時計方向に進み、正のリアクタンスを挿入すると反時計方向に移動することがわかります。また、この軌跡は円を描いていることも見て取れます。  $\Gamma$  opt も同様に、負のリアクタンスに対しては右回りに移動し、正のリアクタンスに対しては左回りに動いていることがわかります。また、この軌跡も円を描いていることがわかります。参考のために、この回路の雑音指数もグラフ化してあります。この回路で雑音指数が最小になるのは、図 4-b の  $\Gamma$  opt が最も  $50\Omega$  に近づいた位置になっています。これはソースインピーダンス(ポート 1 のインピーダンス)が  $50\Omega$  ですから、当然の結果と言えるでしょう。

図4 ソースリアクタンスの装荷特性

# 1.3. 電力整合回路設計

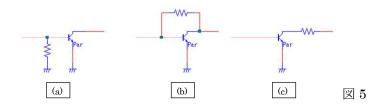

電力整合設計を行う場合、アプリケーションノート No.13 でも述べたように、トランジスタの  $\Gamma$ s、 $\Gamma$ L に入出力のそれぞれのインピーダンスを整合させますが、この場合の条件として K ファクタを 1 以上にする必要があります。このためソースリアクタンスを装荷する前にトランジスタのどこかの位置にロス分(抵抗)を挿入し、この条件を満足させます。抵抗の挿入位置は、図 5 のような 3 箇所がよく用いられます。この 3 つの挿入位置について、電力利得と雑音指数の両方の点から検討を行ってみます。

| 抵抗挿入位置       | 最大有能電力利得[dB] | 最小雑音指数[dB] |

|--------------|--------------|------------|

| (a)ゲート、グランド間 | 16.2         | 2.54       |

| (b)ゲート、ドレイン間 | 13.6         | 1.58       |

| (c)ドレイン、出力間  | 16.2         | 0.46       |

#### 表 1

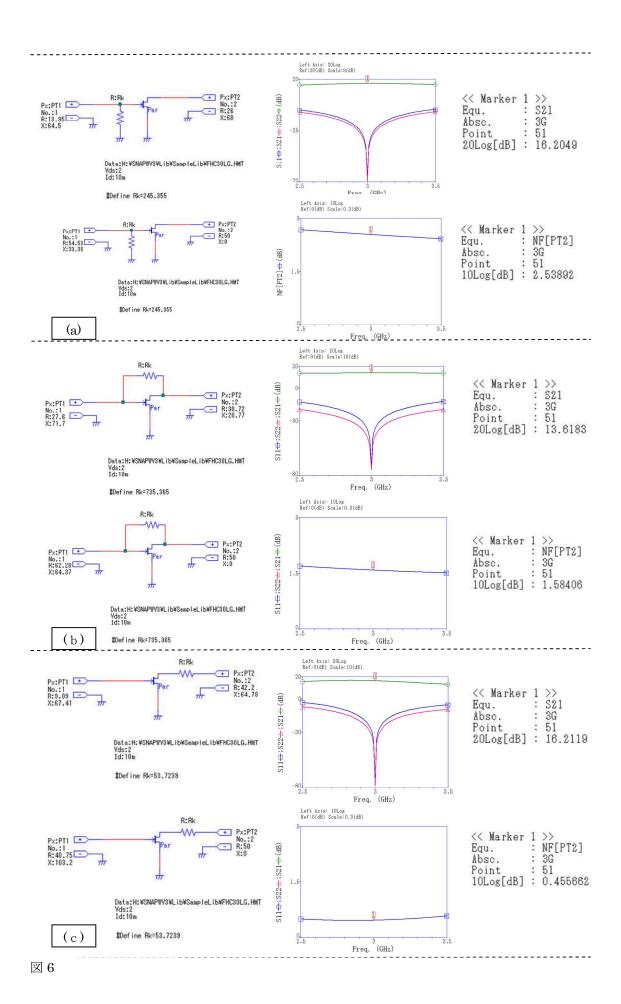

図 6 はそれぞれの抵抗挿入位置において、Kファクタが 1.2 となる抵抗値を求め、その抵抗値での最大有能電力利得と最小雑音指数をシミュレーションしたものです。表 1 に比較を示します。(a)と(c)は利得はほぼ同じですが、雑音指数は(c)の方が格段によくなっています。(b)においては、利得、雑音指数共に(a)と(c)の間にあります。最終回路ではソースリアクタンスの装荷によって利得は減少しますので、利得は大きく雑音指数が小さい(c)の構成が最適になります。パワーアンプの場合は、(c)の抵抗挿入位置は問題になりますが、低雑音増幅器の場合、ドレイン電流は比較的小さいため(C)のようにドレインに直列に挿入しても大きな電力損失にはなりませんので、雑音指数が最も小さくなる(c)の位置に挿入するのが最良であると考えられます。ちなみに、(b)では利得が下がる代わりに広帯域化が期待できます。

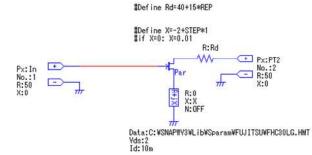

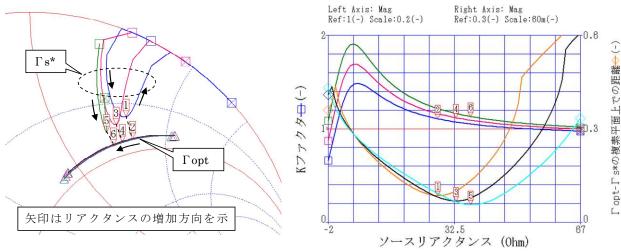

## 1-1-3 ソースリアクタンス値の選定

雑音整合と電力整合を共に成り立たせるには、最大有能電力利得の得られる入力反射の共役値 (以後 $\Gamma$ s\*と呼ぶ) と $\Gamma$ opt が等しくする(もしくは十分近づける)必要があります。 $\Gamma$ s\*は S11 の密接な関数ですので、ソースにリアクタンスを装荷することで、S11 と共に $\Gamma$ s\*も動き ます。したがって、これらの値が最も近づくリアクタンスの値を、前述1-2項の原理を用いて 探します。リアクタンスの値を考える前に、最大有能電力利得について検討します。最大有能 電力利得を得るためには、1·3項で説明したように、Kファクターが1以上で成立しますから、 1以上になるように回路を調整する必要があります。1-3項での検討結果を利用して、図6(c)の構成を用い、ドレインに 50Ωの前後の抵抗を挿入することを検討します。K ファクターの 値はソースリアクタンス値によっても変化しますので、ドレインに挿入する抵抗とソースリア クタンス値の関連を調べてみます。図 7 は Rd 値  $40\Omega$ 、 $55\Omega$ 、 $70\Omega$ においてソースリアクタ ンスの値を $-2\Omega$ ~ $67\Omega$ までスイープした場合の $\Gamma$ opt、 $\Gamma$ s、Kファクタの変化をグラフ化した ものです。スミスチャート上の軌跡は、 $\Gamma$ s の共役値と $\Gamma$ opt をプロットしたもので、ソース リアクタンスの増減に伴い $\Gamma$ s\*が $\Gamma$ opt に近づいてくる様子が覗えます。マーカはそれぞれの Rd 値における最小距離となる位置を示したものです。右側のグラフは、左軸に K ファクタ、 右軸に  $\Gamma$ s\*と  $\Gamma$ opt の複素平面上の距離を示しています。 K ファクタもソースリアクタンスの 値に依存し変化していることがわかります。この結果から、 $\Gamma$ s\*- $\Gamma$ opt 間の距離と K ファク タを考慮しながら、Rd およびソースリアクタンスの値を決定します。今回は以下の値を採用 します。

$Rd = 55\Omega$  $X = 33\Omega$

| マーカ      | Rd[Ohm] | 最小距離  |

|----------|---------|-------|

| [1], [2] | 40      | 0.084 |

| [3], [4] | 55      | 0.067 |

| [5], [6] | 70      | 0.055 |

図 7 ソースリアクタンスの増減による  $\Gamma$ s\*と  $\Gamma$ opt の軌跡

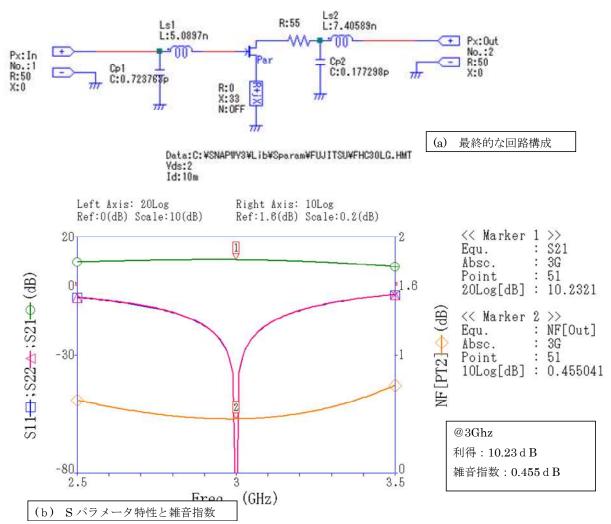

## 1.4. 最終設計

Rd= $55\Omega$ 、ソースリアクタンス X= $33\Omega$ に設定し S パラメータを計算します。その S パラメータを基にして、アプリケーションノート No.13 で紹介した最大有能電力利得の式を用いて、整合回路の反射係数を計算します。その値より必要な入出力のインピーダンスをそれぞれ計算すると、次のようになります。

$$Zs = 34.122 - j72.663[\Omega]$$

$ZL = 160.0 - j211.57[\Omega]$

この値を基に整合回路を設計します。図 8-a は  $\Gamma$ 型で整合回路を設計した例で、図 8-b はその特性を示しています。設計周波数 3GHz において、入出力整合は理想的な値を示しており、雑音指数も 0.46dB(@3GHz)とかなり低く押さえられていることがわかります。このように、FET のソースへの直列帰還リアクタンスの挿入により、雑音整合と電力整合を十分満足できるレベルで両立させることができます。

ここで紹介した設計手法では、回路の  $\Gamma$  opt や  $\Gamma$  s を何度も計算する必要がありますので、これらの値を計算できるシミュレータを用いる必要があります。S-NAP/Design の雑音整合設計は、ここでご紹介したアルゴリズムに基づいて自動的に最終回路までの設計を行うことができます。さらに、ソースリアクタンス挿入に基づいた設計後、リターンロスを緩和し、NFをより低くする簡易オプティマイザーが内蔵されており、容易にさらなる最適値に追い込むことができるようになっています。

図8 最終回路とその特性

(※このシミュレーションには 2005 年発売予定の次期バージョンを用いていますが、現行バージョンでも同様のシミュレーションが可能です。)